# Chapter 9

# The "Long" Metal-Oxide-Semiconductor Field-Effect Transistor

version 2.4 (updated: July 31, 2012), @Prentice Hall

### Outline

- 9.1 The ideal MOSFET

- 9.2 Qualitative operation of ideal MOSFET

- 9.3 Inversion layer transport in the ideal MOSFET

- 9.4 Current-voltage characteristics of the ideal MOSFET

- 9.4.1 The cut-off regime

- 9.4.2 The linear regime

- 9.4.3 The saturation regime

- 9.4.4 DC large-signal equivalent-circuit model of ideal MOSFET

- 9.4.5 Energy band diagrams

- 9.5 Charge-voltage characteristics of ideal MOSFET

- 9.5.1 Depletion charge

- 9.5.2 Inversion layer charge

- 9.6 Small-signal behavior of the ideal MOSFET

- 9.6.1 Small-signal equivalent-circuit model

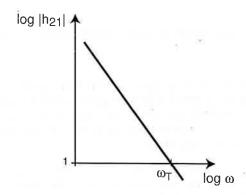

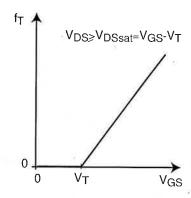

- 9.6.2 Short-circuit current-gain cut-off frequency,  $f_T$ , of ideal MOSFET in saturation

- 9.7 MOSFET non-ideal effects

- 9.7.1 The body effect

- 9.7.2 Effect of back-bias

- 9.7.3 Channel length modulation

- 9.7.4 The subthreshold regime

- 9.7.5 Source and drain resistance

- 9.8 Summary

- 9.9 Further reading

### Advanced Topics

- AT9.1 A more detailed study of inversion layer transport

- AT9.1.1 The sheet-charge approximation

- AT9.1.2 The gradual-channel approximation

- AT9.1.3 Validity of approximations

Problems

The Metal-Oxide-Semiconductor Field-Effect Transistor or MOSFET is arguably the most important semiconductor device ever invented. Integrated circuits based on MOSFETs are ubiquitous in our modern society. There are many that we readily see, such as microprocessors in computers or digital-signal processors in wireless phones, but there are many more that we do not see, such as chips embedded in home appliances, industrial tools, toys, cars, etc. As a result of the explosion of logic ICs, MOSFET technology has become a commodity: it is widely standardized and it is readily available to IC designers around the world. This has fueled, in turn, the widespread use of MOSFETs in many other applications that go beyond logic, such as analog and communications systems. Current examples are wireless LANs, cell phones, and optical fiber transceiver modules, among many others.

There have been many contributors to the conception and development of the MOSFET. Ross postulated in 1955 that an inversion layer could be induced electrostatically by an electrode placed close to the surface of a semiconductor. The first reduction to practice of the MOSFET had to wait until SiO<sub>2</sub> with sufficient quality was developed. The first MOSFET was demonstrated in 1959 by Dawon Kahng and Martin Atalla at Bell Labs. The integrated MOSFET and MOSFET IC's quickly followed. While these represented huge advances in microelectronics, a truly revolutionary event was the invention of CMOS in 1963 by Frank Wanlass at Fairchild. CMOS refers to Complementary MOS, or the pairing of an n-channel MOSFET (based on electrons) and a p-channel MOSFET (based on holes) to form a logic gate. The distinctive feature of CMOS, in contrast with other logic families, is that it performs logic while consuming no DC power. This unique characteristic, perhaps more than anything else, underpins the microelectronics revolution and has led to ultra-large scale integrated circuits. More details about the evolution of MOSFET design and key milestones along the way are given in Sec. 10.5.6.

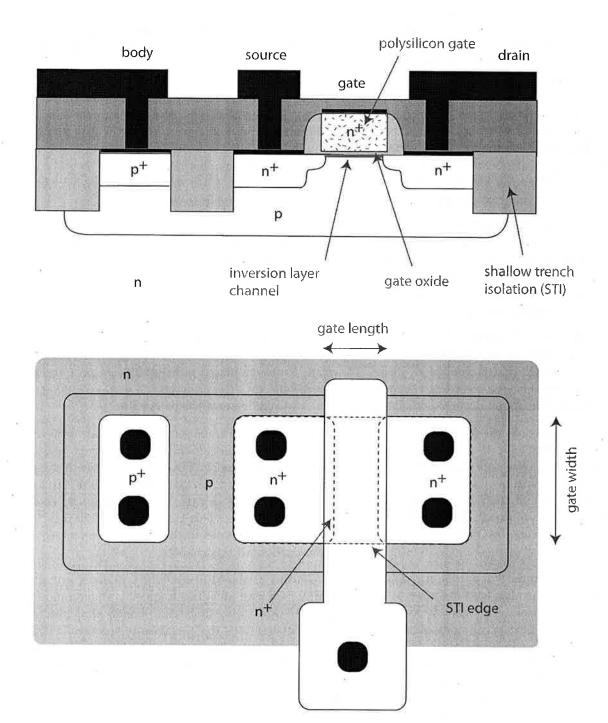

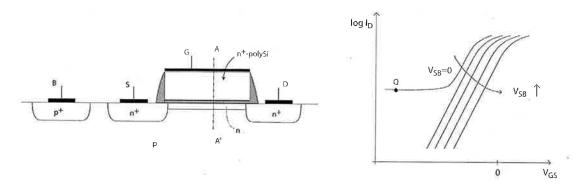

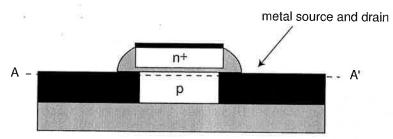

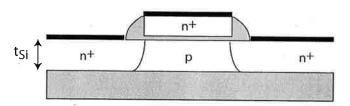

A schematic cross section of a modern integrated n-channel MOSFET is shown in Fig. 9.1. At its heart, the MOSFET consists of a metal-oxide-semiconductor structure with an  $n^+$ -region on each side. The metal of the MOS structure is referred to as gate. The two  $n^+$ -regions are referred to as source and drain. The p-type well surrounding the device is referred to as body. A MOSFET is a four-terminal device. The gate, source, drain, and body regions are all contacted separately. In modern technology, the gate is made out of  $n^+$ -polySi and it is typically silicided on top to reduce its resistance. The surface of the source and drain, as well as the body contact, are all silicided for the same reason. To facilitate electrical contact, a  $p^+$ -region is implanted at the surface of the body contact. The device is isolated through shallow trenches that cut below the heavily-doped regions of the source, drain, and body. In the planar view shown at the bottom of Fig. 9.1 two key dimensions are defined.  $Gate\ length$  and  $gate\ width$  refer to the length and width of the intrinsic portion of the device defined by the overlap of the polySi gate and the area enclosed by the shallow trench isolation. These are critical dimensions with a major impact on most electrical figures of merit of the MOSFET.  $^1$

The complementary p-channel MOSFET looks similar with p and n regions interchanged. Its operation is similar to that of the n-channel MOSFET but the signs of voltages and currents are reversed. Since it is based on hole transport, the p-channel MOSFET has lower performance.

The heart of the MOSFET is the intrinsic region, also referred to as channel region. This

<sup>&</sup>lt;sup>1</sup>Notice the odd choice of notation: the width of the gate tends to be larger than its length. This is for historical reasons.

Figure 9.1: Simplified schematic diagram of a modern MOSFET: cross section (top), layout at the wafer surface (bottom).

is the MOS portion of the device directly underneath the gate between source and drain. The rest is often referred to as the extrinsic portions of the MOSFET. When a gate voltage in excess of the threshold voltage is applied to the gate of the MOS structure, an inversion layer forms in the semiconductor right below the oxide/semiconductor interface. By virtue of the existence of a finite overlap of the gate above the n<sup>+</sup> source and drain regions (this is very important to insure low parasitic resistance), the inversion layer creates a conducting channel that connects the source and the drain. If a positive voltage is applied to the drain with respect to the source, electrons will flow from the source to the drain through the inversion layer. When the gate voltage is brought below the threshold voltage, there is no inversion layer in the MOS structure and the conducting path between source and drain is broken. In this manner, the MOSFET behaves as a switch. Electron flow from source to drain is controlled by the gate voltage; it is enabled when the gate voltage is above threshold and it is forbidden in the opposite case.

The MOSFET can also behave as an amplifier. With the gate voltage above threshold and an inversion layer connecting source and drain, the higher the gate voltage, the more electrons are induced in the inversion layer, and the higher the current that flows between source and drain. As we will study in this chapter, under the right conditions, the current between the source and drain can be made independent of the drain voltage. This "isolation between input and output" is an essential property of a good amplifying device.

A word on notation. In most cases, a MOSFET features a rather symmetrical design. The source and drain are interchangeable. What makes the source and the drain be identified as such is the voltage that is applied to them. The drain is always biased positive with respect to the source. In this way, electrons flow out of the source and into the drain. If the voltage difference between source and drain was to change its sign, we would change the names too.

In this book, the MOSFET is presented in two chapters. The present chapter deals with the "long" MOSFET, while the next one is concerned with the "short" MOSFET. The terms "short" and "long" refer to length of the gate of the transistor (marked in Fig. 9.1). As we will learn, these are somehow relative terms to other key dimensions of the device. Modern MOSFETs are very small and they are getting smaller all the time. Because of this, understanding the short MOSFET is of great importance for microelectronics engineers. This is the topic of Chapter 10. Before the short MOSFET can be productively attacked, one has to develop a clear picture of the operation of the "long" MOSFET. This is the purpose of this chapter.

The chapter starts with a definition of the concept of the ideal MOSFET. This is a useful simplification that captures the essence of the MOSFET and allows us to quickly understand its basic operation. The ideal MOSFET is amenable to developing first-order models that provide substantial physical insight. Section 9.2 qualitatively describes the operation of the ideal MOSFET using a simple water analogy. Basic physics of electron transport in the inversion layer are discussed in Section 9.3. Section 9.4 proceeds to describe the current-voltage characteristics of the ideal MOSFET and develops a simple analytical model for it. Section 9.5 presents the charge-voltage characteristics of the ideal MOSFET. After that, Section 9.6 discusses its small-signal behavior in the saturation regime which is the most useful regime of operation. The chapter ends with a section on the most important non-ideal effects of the long MOSFET.

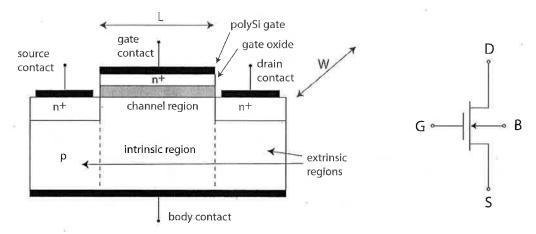

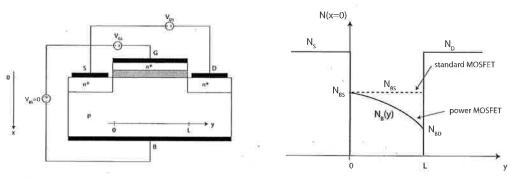

Figure 9.2: Left: sketch of the cross section of an ideal MOSFET. This conceptual device is a good basis for developing first-order understanding and models for MOSFET operation. Right: Circuit symbol for a MOSFET.

### 9.1 The ideal MOSFET

As in other chapters in this book, it is of great usefulness to define the concept of the ideal MOSFET. This is a model device that captures the essence of the MOSFET but hides away complicating details and second-order effects. The ideal MOSFET is a useful framework on top of which to construct a solid understanding and a useful set of models for the MOSFET. This will be of great value in this chapter about the long MOSFET, but also in Ch. 10 when studying the short MOSFET.

A sketch of the ideal MOSFET is shown in Fig. 9.2. This is a perfectly symmetrical device. It consists of uniformly doped source, drain, gate, and body regions. The edges of the source and drain n<sup>+</sup>-regions are perfectly lined up with the edges of the MOS structure. The body contact is made at the bottom of the device.

The ideal MOSFET contains a number of simplifying assumptions:

- The MOS structure is ideal as defined in Ch. 8.

- All carrier flow is one dimensional.

- Doping levels are uniform throughout.

- We assume Maxwell-Boltzmann statistics (non degenerate).

- Electron transport along the inversion layer takes place only by drift (i.e., we neglect diffusion).

- Electrons drift along the inversion layer in the mobility regime, *i.e.*, the electron velocity is proportional to the lateral electric field along the inversion layer. We undo this assumption in Ch. 10.

- We neglect the *body effect*, that is, the dependence of the threshold voltage on the space coordinate along the channel. This is fixed in Sec. 9.7.1.

- We ignore any resistance effects associated with the quasi-neutral regions or the ohmic contacts to these regions. The impact of parasitic source and drain resistance is discussed in Sec. 9.7.5.

- We ignore any effects associated with the sidewall of the source-body and drain-body junctions. This implies that the extent of the depletion region underneath the MOS structure is assumed to be unaffected by the presence of the source and drain regions. The impact of this on the electrostatics of the channel is discussed in Sec. 10.2.

- We ignore the saturation current of the reverse biased source/body and drain/body PN junctions.

- There are no three-dimensional effects, that is, the device scales perfectly with its width.

- We ignore any effects associated with the substrate that surrounds the transistor (not shown in Fig. 9.2), including the presence of a PN junction with the MOSFET body with rectifying I-V characteristics.

- We neglect impact ionization anywhere in the device. Its role is discussed in Sec. 10.4.2.

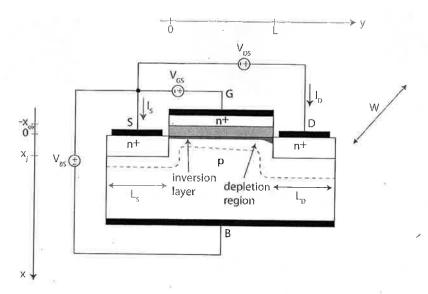

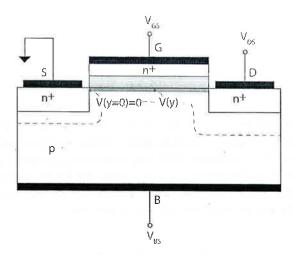

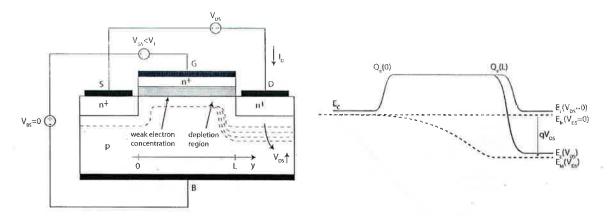

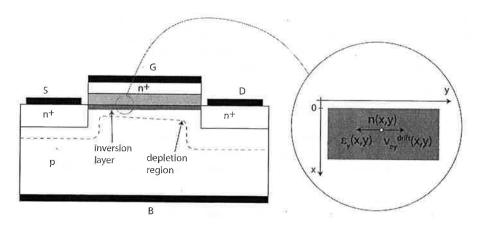

Fig. 9.3 shows a cross section of the ideal MOSFET indicating the coordinate axis convention used here. The x axis is selected into the wafer with its origin at the semiconductor surface. The y axis is selected along the channel from source to drain with its origin at the source edge. Indicated is also the inversion layer and the depletion region that under the right conditions exist underneath the source, channel, and drain regions of the device. This figure suggests that the depletion regions of the source and drain merge with that of the channel at the edges of the channel. This is obviously the case. However, in our ideal MOSFET we assume that the depletion region underneath the channel is of uniform thickness throughout. That is, we neglect any effect of the source and drain sidewalls.

Fig. 9.3 also shows the voltage and current notations that are used in this book. All voltages are referred to the source. As usual, entering terminal currents are positive. In our ideal MOSFET, the gate and body currents are assumed zero. Hence, the source current is equal to minus the drain current.

# 9.2 Qualitative operation of the ideal MOSFET

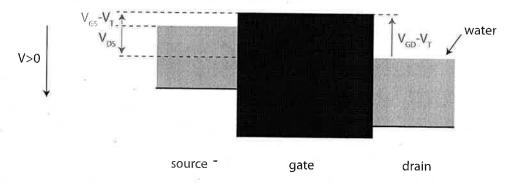

The operation of the MOSFET can be qualitatively understood by establishing an analogy with a water reservoir system, as sketched in Fig. 9.4. In this analogy, the source and drain can be thought of as water reservoirs with a relative height that can be adjusted. The gate plays the role of barrier separating the two water reservoirs. The relative height of the two reservoirs of water corresponds to the drain to source voltage. The higher  $V_{DS}$ , the lower the level of the water on the drain is with respect to that of the source. The relative height of the barrier above the water

Figure 9.3: Sketch of the cross section of an ideal MOSFET defining spatial coordinates as well as voltage and current notation. Shown are also sketches of the inversion layer and the depletion region that under appropriate conditions exist underneath the source, gate and drain.

level of the source corresponds to the gate to source voltage in excess of threshold. The higher  $V_{GS}$ , the lower the gate barrier. At a value of  $V_{GS} = V_T$ , the top of the barrier is level with the water surface. In this analogy, we ignore the effect of the MOSFET body.

The water analogy of the MOSFET reveals three possible regimes of operation. These are sketched in Fig. 9.5. When the barrier level is above the water level on the source, water cannot flow between source and drain. This is shown on the left of this figure. This occurs regardless of the relative levels of the source and drain water surfaces. In the MOSFET, this corresponds to the *cut-off* regime with  $V_{GS} < V_T$ . In the cut-off regime, there is no inversion layer under the gate and  $I_D = 0$  regardless of the value of  $V_{DS}$ .

Figure 9.4: Sketch of ideal MOSFET and a water analogy. The source and drain can be thought of as pools of water separated by a barrier. The drain to source voltage is equivalent to the relative heights of the water levels in the two pools of water. The gate to source voltage above threshold is equivalent to the relative height of the barrier above the water level on the source.

Figure 9.5: Regimes of operation of the water analogy of the MOSFET. The drain water level is always below the source water level. In the cut-off regime (left), the barrier is above the water level on the source and drain and water does not flow. In the triode or linear regime (middle), the barrier is below the water level of both the source and drain. Water flows from source to drain. In the saturation regime (right), the barrier is below the water level of the source but above that of the drain. Water flows from source to drain, but the water current is independent of the relative levels of source and drain.

A second regime of operation corresponds to the case depicted in the middle of Fig. 9.5. When the barrier is below the water levels of the source and drain, water flows above the barrier from one reservoir to the other. It is clear that in this case, the higher the water level difference between source and drain, or the lower the barrier level with respect to the water surfaces, the higher the current too. In the MOSFET, this situation corresponds to the linear regime, also called the triode regime. In this mode of operation,  $V_{GS} > V_T$  and  $V_{GD} > V_T$ . As a consequence, an inversion layer is formed below the gate that constitutes a path that connects the source and drain. With  $V_{DS} > 0$ , an electric field is created along the inversion layer and electrons drift from source to drain. As in the water analogy, the current flowing through the channel depends both on  $V_{DS}$  and  $V_{GS}$ . If  $V_{DS}$  increases, the lateral electric field along the inversion layer increases and the current increases. If  $V_{GS}$  increases, the amount of electrons induced in the inversion layer increases and the current also increases.

Finally, the third regime of operation of the MOSFET is depicted on the right of Fig. 9.5. In this regime, the top of the barrier is below the water level on the source but above the water level on the drain. Water still can flow over the barrier, but there is a key difference with the regime in the middle of the figure. The water flow is independent of the relative height of the water level on the drain side with respect to the source. As the water flows over the barrier, when it reaches the end, it simply falls down freely. Lowering the water level at the drain does not increase the flow of water.

In the MOSFET, this regime of operation corresponds to a situation in which  $V_{GS} > V_T$  but  $V_{GD} < V_T$ . As we will see, this creates an inversion layer at the surface of the semiconductor that thins down along the channel. As in the water analogy, the electron velocity increases along the channel from source to drain. At the drain side of the channel, it is said that the inversion layer is pinched off. The electrons simply "drop" into the drain. The remarkable aspect of this regime is that once  $V_{DS}$  is high enough for this regime to be established, the drain voltage has no further impact on the electric field that is set up along the channel. Beyond this value of  $V_{DS}$ , referred to as  $V_{DSsat}$ , the electric field in the channel is only affected by  $V_{GS}$ . In consequence, the channel current is independent of  $V_{DS}$ . This is called the saturation regime and it is the most important regime of operation of the MOSFET. It is in the saturation regime where a MOSFET is biased as an amplifier.

Armed with this qualitative understanding, we are now in a position to start looking in a more rigorous manner at the physics of the MOSFET in its various regimes of operation and start developing models for it. The next section discusses the physics of electron transport along the inversion layer which is at the heart of the MOSFET operation.

# 9.3 Inversion layer transport in the ideal MOSFET

The first step in the construction of a model for the ideal MOSFET is to develop a suitable formulation for electron transport in the inversion layer. While this is fairly straightforward, there are some subtleties to it. A detailed study is presented in Advanced Topic AT9.1. This section captures the most important results.

In the inversion layer of a MOSFET under normal operation, electrons are trapped in a potential barrier that prevents them from escaping to the gate or the body. In consequence, electron transport only takes place laterally along the surface of the semiconductor from source to drain, right under the gate oxide. In this situation, there is no compelling interest in describing the behavior of electrons as a function of the normal direction into the semiconductor (the x direction). The vertical dimension can be abstracted away by integrating the electron concentration across the inversion layer. So, instead of thinking of n(x, y), the electron concentration as a function of location in x and y at any one location in the inversion layer, it is much more productive to think of the sheet carrier concentration in the inversion layer,  $n_s(y)$ , at a particular location along the channel, where:

$$n_s(y) = \int_0^\infty n(x, y) dx \tag{9.1}$$

$n_s$  has units of  $cm^{-2}$ . This integrates all electrons in the inversion layer at a location y and ignores their detailed distribution in x. The upper integration limit in this integral can be extended to  $\infty$  without introducing any problems because the electron concentration peaks at the surface and drops very fast with x.

With the MOSFET biased in one of its conducting regimes, the electron current along the inversion layer can be easily expressed in terms of  $n_s$ . In the ideal MOSFET, we assume that electron flow takes place by drift and we neglect any electron diffusion (see Advanced Topic AT9.1). Under this assumption, the electron current is simply given by the product of the electron charge, the electron velocity, and the sheet electron concentration, times the width of the device:

$$I_e \simeq -qW v_{ey}(y) n_s(y) \tag{9.2}$$

where  $v_{ey}$  is the average velocity for the electrons in the inversion layer in the y direction from source to drain. Note that while  $v_{ey}$  and  $n_s$  depend on y,  $I_e$  does not. This is a consequence of the fact that electrons cannot escape from the channel and must all flow from source to drain.

Eq. 9.2 can also be written in terms of the sheet charge density of the inversion layer,  $Q_i$ . This is related to  $n_s$  through:

$$Q_i(y) = -qn_s(y) (9.3)$$

In terms of  $Q_i$ , Eq. 9.2 becomes:

$$I_e \simeq W v_{ey}(y) Q_i(y) \tag{9.4}$$

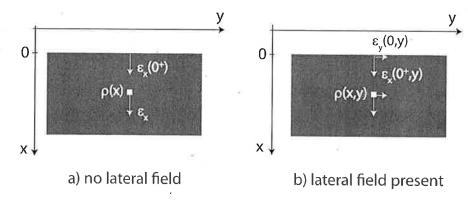

In more rigorous terms, the key assumption that led us to Eqs. 9.2 and 9.4 is called the sheet-charge approximation (SCA). This approximation makes it physically meaningful to define an average lateral velocity for all the electrons in the inversion layer. Intuitively, this is possible whenever the distribution of lateral velocities in depth does not change too rapidly in the scale of the changes that are taking place in the electron concentration. It essentially requires that the inversion layer be very thin in the scale of other normal dimensions of the MOS structure (the oxide thickness and the thickness of the depletion region underneath the inversion layer). This is discussed in detail in Advanced Topic AT9.1.

According to our definition of the ideal MOSFET, we consider that the lateral electric field along the inversion layer is small enough for electrons to drift in the mobility regime. In this regime, the lateral electron velocity is proportional to the lateral electric field. As it turns out, this assumption is quite poor in MOSFETs of any gate length. Nevertheless, it is important and useful to proceed with this assumption for a while as the resulting models are an excellent starting point for a more detailed study of the MOSFET. We will undo this assumption and study the impact of velocity saturation in Ch. 10. In the mobility regime, we then have:

$$v_{ey}(y) \simeq -\mu_e \mathcal{E}_y(y) \tag{9.5}$$

where  $\mathcal{E}_y(y)$  is the average longitudinal electric field in the inversion layer. In this regime, Eq. 9.4 becomes:

$$I_e \simeq -W\mu_e \mathcal{E}_y(y)Q_i(y) \tag{9.6}$$

An alternate way to express Eq. 9.6 is in terms of the voltage V(y) of the inversion layer. Since the source is our reference for all voltages, we define V as the surface potential at a location y with respect to the surface potential at the source-end of the channel:

$$V(y) = \phi_s(y) - \phi_s(y = 0)$$

(9.7)

The lateral electric field in the inversion layer can now be expressed in terms of V:

$$\mathcal{E}_y(y) = -\frac{d\phi_s(y)}{dy} = -\frac{dV(y)}{dy} \tag{9.8}$$

Inserting Eq. 9.8 into 9.6 yields:

$$I_e = W\mu_e Q_i(y) \frac{dV(y)}{dy} \tag{9.9}$$

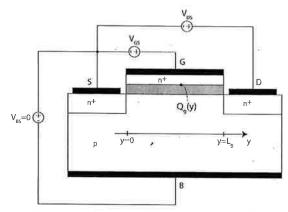

To make further progress we need to find a way to relate  $Q_i(y)$  with V(y). The gradual-channel approximation (GCA) allows us to do that. Before we introduce this approximation, it is necessary to remember the fundamental charge control relationship of the inversion layer in inversion. This was studied in Chapter 8. In a two-terminal MOS structure under inversion, the charge in the inversion layer is to the first order determined by the voltage applied to the gate with respect to the source in excess of the threshold voltage:

$$Q_i = -C_{ox}(V_{GS} - V_T) (9.10)$$

This expression was derived for a MOS structure with the source as voltage reference and with the body tied up to the source  $(V_S = V_B = 0)$ . In this case, the inversion layer voltage is zero everywhere and as a consequence, the inversion layer charge is uniform across the structure. In a MOSFET, unlike the simpler two-terminal MOS structure, this expression only applies at the source end of the channel, where V = 0. Anywhere else down the channel, V is different from zero and this expression needs to be reformulated.

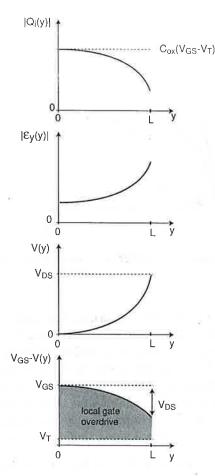

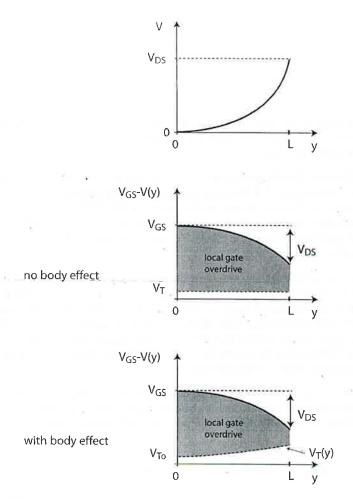

The GCA allows us to recycle expression 9.10 to situations in which V changes in space but it does so relatively slowly. The key assumption is that at any one location, the inversion layer charge is only set by the local vertical electrostatics with the lateral electrostatics having a negligible effect on it. This means that we can reuse Eq. 9.10 provided that we subtract the local voltage of the inversion layer, V(y), which in general is not zero. This is sketched in Fig. 9.6. This figure shows that the voltage difference between the gate and the inversion layer at a location y is in general  $V_{GS} - V(y)$ , instead of simply  $V_{GS}$ . The inversion layer charge at that location, under the GCA is then given by:

$$Q_i(y) \simeq -C_{ox}[V_{GS} - V(y) - V_T]$$

(9.11)

The GCA effectively breaks up the two-dimensional electrostatics of the MOSFET into two simpler one-dimensional problems: the vertical electrostatics control the charge in the inversion layer, while the lateral electrostatics control its lateral flow along the channel. In the GCA, the lateral electrostatics represent a relatively "small" perturbation of the vertical electrostatics. As a consequence, the inversion layer charge at any one location can be computed using the one-dimensional MOS theory developed in the previous chapter, with the simple precaution of using the local inversion layer voltage, V(y), instead of V=0.

Advanced Topic AT9.1 discusses the GCA and the SCA in more detail and explores the limits of applicability of these two approximations. It is shown that for the GCA to apply, the lateral electric field must be smaller than an "effective" vertical electric field. In turn, this demands that the aspect ratio of the device be large enough, that is, that the channel length be sufficiently

Figure 9.6: Schematic diagram of a-MOSFET illustrating local gate voltage overdrive.

longer than a vertical characteristic length. In AT9.1 it is also shown that if the GCA is fulfilled, the SCA also applies.

Eq. 9.11 allows us to formulate the MOSFET current equation in terms of a single variable, V(y). Plugging Eq. 9.11 into 9.9, we get:

$$I_e = -W\mu_e C_{ox} [V_{GS} - V_T - V(y)] \frac{dV(y)}{dy}$$

(9.12)

This is a first-order differential equation in terms of V(y). Its solution with appropriate boundary conditions yields the channel current in the ideal MOSFET under a variety of conditions.

# 9.4 Current-voltage characteristics of the ideal MOSFET

In the previous section, we developed a quasi-1D formulation for inversion layer transport in a MOSFET. This is the basis for a first-order formulation of the current-voltage characteristics of the MOSFET under the cut-off, linear and saturation regimes. This is carried out in the next three subsections.

### 9.4.1 The cut-off regime

The cut-off regime is defined for values of  $V_{GS} < V_T$  and  $V_{DS} \ge 0$ . In a simple first-order formulation, since  $V_{GS}$  is below threshold, there is no inversion layer and the current is zero, regardless of the value of  $V_{DS}$ . In the cut-off regime, the transistor is off. This is one of the two logic states in which a MOSFET is biased when operating as a switch.

Figure 9.7: Sketch of MOSFET in linear regime and with no back-bias.

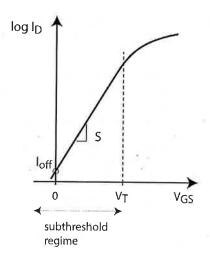

To the second order, we know that below threshold, there are still electrons at the surface of the semiconductor. We have referred to it as the weak inversion regime of the MOS structure or the subthreshold regime. As a consequence, even for  $V_{GS} < V_T$ , there will be a small amount of current flowing through the MOSFET. This is the *subthreshold regime* of operation of the MOSFET and it will be discussed in Section 9.7.4 below.

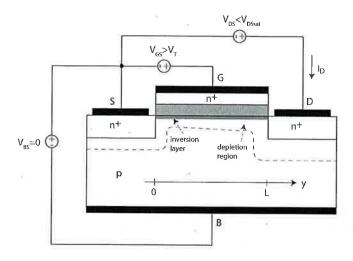

### 9.4.2 The linear regime

The linear regime is defined for values of  $V_{GS} > V_T$  and  $V_{GD} > V_T$ . This situation is sketched in Fig. 9.7. Under these conditions, an inversion layer extends all the way under the gate from source to drain, a lateral field is set up along the inversion layer, and current flows.

With our current understanding, we should expect the drain current in the linear regime to increase with  $V_{GS}$  and  $V_{DS}$ , but for different reasons. All things being equal, if  $V_{GS}$  increases, the inversion layer charge increases in absolute magnitude and the channel current must increase along with it. On the other hand, if  $V_{DS}$  increases, the electric field along the channel is also enhanced as a result, and more channel current ought to flow. This behavior resembles that of the triode vacuum tube and for this reason, the linear regime is also referred to as the triode regime.

Deriving an expression for the current-voltage characteristics of the MOSFET in the linear regime is fairly straightforward. We start where we left off in the previous section, with Eq. 9.12. Solving this differential equation in this case is rather easy. By bringing dy to the left-hand side, variable separation is achieved:

$$I_e dy = -W \mu_e C_{ox} (V_{GS} - V_T - V) dV$$

(9.13)

We can then integrate the left-hand side along the channel from y = 0 to y = L, and the

right-hand side from V = 0 to  $V = V_{DS}$ , to get:

$$I_e \int_0^L dy = -W \mu_e C_{ox} \int_0^{V_{DS}} (V_{GS} - V_T - V) dV$$

(9.14)

or, after integration,

$$I_e = -\frac{W}{L} \mu_e C_{ox} (V_{GS} - V_T - \frac{1}{2} V_{DS}) V_{DS}$$

(9.15)

Going from channel current to drain terminal current is simple. Since electrons flow through the inversion layer from source to drain, this must necessarily result in an entering drain terminal current which, under standard sign convention, is positive. Since in our choice of y axis,  $I_e$  is negative, we therefore need to apply a negative sign. The drain current is then:

$$I_D = \frac{W}{L} \mu_e C_{ox} (V_{GS} - V_T - \frac{1}{2} V_{DS}) V_{DS}$$

(9.16)

This equation gives the current-voltage characteristics of the ideal MOSFET in the linear regime. Before graphing it for different values of  $V_{DS}$  and  $V_{GS}$ , we must understand its limits of applicability. Eq. 9.16 was derived under the assumption that the inversion layer extends underneath the entire channel. However, the charge distribution in the inversion layer is not uniform along the channel: it drops in absolute magnitude from source to drain. This is because V increases along the inversion layer from 0 to  $V_{DS}$  and, as a result,  $Q_i$  is reduced in absolute magnitude (see Eq. 9.11). This is discussed in detail later on in this section. The lowest inversion layer charge occurs at the drain end of the device where it is given by:

$$Q_i(y=L) = -C_{ox}(V_{GS} - V_T - V_{DS})$$

(9.17)

For  $|Q_i(y=L)| > 0$ ,  $V_{DS} < V_{GS} - V_T$  must be satisfied. This is the restriction on Eq. 9.16.

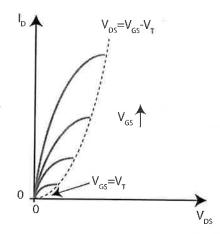

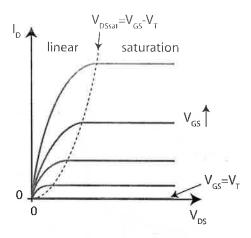

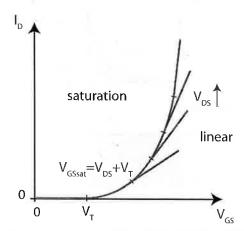

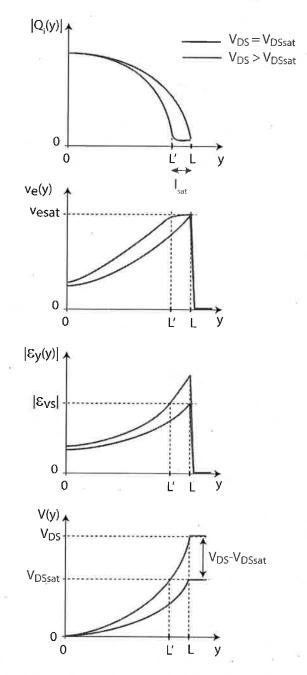

Under this constraint, Eq. 9.16 is graphed in Fig. 9.8 which sketches  $I_D$  as a function of  $V_{DS}$  for different values of  $V_{GS}$ . The linear regime is the area of this graph comprised by the vertical axis and the line labeled " $V_{DS} = V_{GS} - V_T$ ." There are several features in this graph that are worth noting. First, for a given value of  $V_{GS}$ ,  $I_D$  increases with  $V_{DS}$ . Initially the increase is relatively fast but then it appears to saturate. The reason for the increase was mentioned before: a higher  $V_{DS}$  results in a larger lateral field and a larger current. The reason for the saturation will be discussed below. Second, for a given value of  $V_{DS}$ ,  $I_D$  increases with  $V_{GS}$ . This was also expected. A higher  $V_{GS}$  induces a higher concentration of electrons in the inversion layer that results in increased current. Finally, for  $V_{GS} = V_T$ .  $I_D = 0$ . as it is to be expected since the inversion layer disappears. Notice that for  $V_{GS} = V_T$ , the model only applies for  $V_{DS} = 0$  for which  $I_D = 0$  anyway.

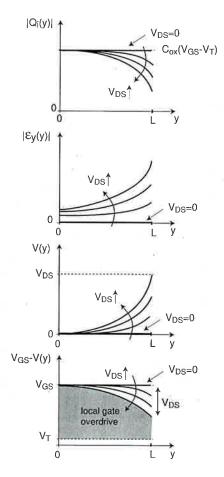

In order to better understand the physics of the MOSFET in the linear regime, in particular, its saturating behavior as  $V_{DS}$  increases, Fig. 9.9 sketches  $|Q_i(y)|$ ,  $|\mathcal{E}_y(y)|$ , |V(y)|, and  $|V_{GS}| - |V(y)|$

Figure 9.8: Sketch of I-V characteristics of a MOSFET in the linear regime. Each line corresponds to a different value of  $V_{GS}$ .

along the channel of the MOSFET from source to drain. The mathematical expressions for these parameters as a function of y are easy to derive (see Problem 9.2). As Fig. 9.9 indicates,  $Q_i$  drops in absolute magnitude along the channel from source to drain. This is because V increases along the channel from a value of zero at the source, to  $V_{DS}$  at the drain. This "debiases" the inversion layer as we proceed from source to drain. In order to maintain a constant current,  $\mathcal{E}_y(y)$  must increase in magnitude from source to drain so that there is an increasing electron velocity. This yields a voltage distribution along the channel that is superlinear in y. The amount of local "gate overdrive,"  $V_{GS} - V(y) - V_T$ , is reduced along the channel from source to drain.

It is illuminating to consider how the profiles of Fig. 9.9 change as  $V_{DS}$  increases. This is shown in Fig. 9.10. For  $V_{DS}=0$ , the lateral field across the inversion layer is zero and the electron concentration is uniform. For low values of  $V_{DS}$ , a nearly uniform electric field is set along the channel and the voltage distribution is nearly linear. As  $V_{DS}$  increases, the lateral electric field increases but the drain-end of the device starts getting debiased, that is, the electron concentration towards the drain end of the channel drops as y approaches L. For large  $V_{DS}$ , channel debiasing becomes severe. The electron concentration on the drain-side of the channel drops very low and the majority of the voltage is absorbed there.

To understand how channel debiasing results in current saturation, one must focus on its effect on the situation at the source end of the channel. Towards understanding this, it is useful to go back to the very fundamental Eq. 9.4 that expressed the channel current at any one location as the product of the channel charge times the electron velocity at that particular location. At the source end of the channel (y = 0), this expression becomes:

$$I_e \simeq W v_{ey}(0) Q_i(0) \tag{9.18}$$

We can write an equation like this for any location of the channel. What is significant about the source end is that the inversion layer charge there is set <u>only</u> by  $V_{GS}$  through:

Figure 9.9: Inversion layer charge, lateral electric field, channel voltage and local gate overdrive as a function of location along the channel for a MOSFET biased in the linear regime.

$$Q_i(0) = -C_{ox}(V_{GS} - V_T) (9.19)$$

since V(0) = 0. In particular,  $Q_i(0)$  is independent of what happens down the channel.

The  $V_{DS}$  dependence enters Eq. 9.18 through the electron velocity,  $v_{ey}(0)$ . This is set by the local lateral electric field. With transport in the mobility regime:

$$v_{ey}(0) \simeq -\mu_e \mathcal{E}_v(0) \tag{9.20}$$

The key to understanding the saturating behavior of  $I_D$  with  $V_{DS}$  is to focus on the  $V_{DS}$  dependence of  $\mathcal{E}_y(0)$ . As Fig. 9.10 shows, as  $V_{DS}$  increases, so does the electric field at the source. However, when channel debiasing becomes prominent at high  $V_{DS}$ , the rise of  $\mathcal{E}_y(y)$  slows down as higher values of  $V_{DS}$  are applied and eventually it does not increase any more. In consequence, at high  $V_{DS}$ , the velocity at which electrons are extracted from the source saturates

Figure 9.10: Inversion layer charge, lateral electric field, channel voltage and local gate overdrive as a function of location along the channel for a MOSFET biased in the linear regime for increasing values of  $V_{DS}$ . For high  $V_{DS}$ , channel debiasing at the drain-end of the channel is apparent.

and so does the current.

This line of argumentation is productive in one more and very general way. In the MOSFET, when dealing with transport phenomena, it is often most useful to focus on what is happening on the source side, as opposed to the drain side of the channel. It is at the source end of the channel that we can think in terms of the number of electrons that are extracted from the source and the velocity at which they come out. This is a simple and powerful picture that often provides great physical insight.

It is also interesting to reflect on what is going on at the drain-end of the channel as  $V_{DS}$  approaches  $V_{GS} - V_T$ . This is the point with the lowest concentration of electrons in the inversion layer. As  $V_{DS}$  approaches  $V_{GS} - V_T$ , Eq. 9.17 indicates that  $Q_i$  goes to zero at y = L. In this limiting case, the location at the drain end of the channel is known as the *pinch-off* point. Complete depletion of electrons is of course not possible, otherwise, the current could not flow. What is happening and how could our formalism deal with it?

There are several problems with our formalism close to y=L for values of  $V_{DS}$  that approach  $V_{GS}-V_T$ . First of all, at  $y\simeq L$  for  $V_{DS}\simeq V_{GS}-V_T$ , the local gate overdrive goes to zero. As a consequence, the fundamental charge control relationship stops applying and the gradual-channel approximation fails. This should make the use of Eq. 9.17 suspect. An additional problem with our formalism around the pinch-off condition is that the assumption of linearity between electric field and electron velocity is unlikely to apply as the lateral field gets high enough for velocity saturation to occur. For these reasons, the current-voltage characteristics given by Eq. 9.16 do not apply when  $V_{DS}$  approaches  $V_{GS}-V_T$ .

Developing a detailed model of current transport at the drain-end of the channel when  $V_{DS}$  approaches and exceeds  $V_{GS} - V_T$  is a major challenge. Fortunately, for a first-order analysis, we do not need to do it. The reason is that the model embodied in Eq. 9.16 is fairly accurate over nearly the entire range of drain current. This is understood by examining Fig. 9.8 in detail. For small values of  $V_{DS}$ , increasing  $V_{DS}$  brings about a significant increase in  $I_D$ . For higher values of  $V_{DS}$ , however, a further increase in  $V_{DS}$  produces a proportionally smaller increase in  $I_D$ . For  $V_{DS}$  values close to  $V_{GS} - V_T$ ,  $I_D$  is essentially saturated. The origin of this diminishing return in  $I_D$  for high values of  $V_{DS}$  is the "channel debiasing" discussed above. Even before we reach pinch-off and the simple model developed above becomes invalid, the drain current has essentially stopped increasing.

It is not difficult to quantify how close  $V_{DS}$  can get to  $V_{GS} - V_T$  before the simple model developed above fails. As Problem 9.3 shows, for typical MOSFET designs,  $V_{DS}$  can get up to about 80% of  $V_{GS} - V_T$  before the gradual-channel approximation fails. This means that  $I_D$  can build up to about 96% of the maximum value predicted by Eq. 9.16 and still be fairly accurate.

Exercise 9.1: Consider a long n-channel MOSFET characterized by the following parameters:  $n^+$ -polysilicon gate ( $W_M = \chi_S = 4.04 \text{ eV}$ ),  $x_{ox} = 15 \text{ nm}$ , uniform  $N_A = 10^{17} \text{ cm}^{-3}$ ,  $L = 1 \text{ }\mu\text{m}$ ,  $W = 10 \text{ }\mu\text{m}$  at a bias given by  $V_{GS} = 2.5 \text{ }V$ ,  $V_{DS} = 1 \text{ }V$ , and  $V_{BS} = 0$ . Estimate the sheet charge density in the inversion layer at the source- and drain-ends of the channel. Estimate the current flowing through the drain of this transistor. Use  $\mu_e = 500 \text{ cm}^2/V.s.$

Proceeding as in Ch. 8, for this MOS structure we can easily find:  $C_{ox}=2.3\times 10^{-7}~F/cm^2$ ,  $\gamma=0.79~V^{1/2},~\phi_{sT}=0.84~V,~V_{FB}=-1~V,~{\rm and}~V_T=0.56~V.$

To obtain the sheet charge density at the source-end of the channel at the indicated bias, we can use Eq. 9.19:

$$Q_i(0) = -C_{ox}(V_{GS} - V_T) = -2.3 \times 10^{-7} \ F/cm^2 \ (2.5 - 0.56) \ V = -4.5 \times 10^{-7} \ C/cm^2$$

Before we can obtain the corresponding value at the drain-end of the channel, we need to assert the regime of operation of the transistor. For the indicated bias,  $V_{GS} - V_T = 1.94 \ V > V_{DS} = 1 \ V$ . Hence this MOSFET is biased in the linear regime. We can then use Eq. 9.17 to obtain:

$$Q_i(L) = -C_{ox}(V_{GS} - V_T - V_{DS}) = -2.3 \times 10^{-7} \ F/cm^2 \ (2.5 - 0.56 - 1) \ V = -2.2 \times 10^{-7} \ C/cm^2$$

The drain current can be obtained from Eq. 9.16:

$$I_D = \frac{W}{L} \mu_e C_{ox} (V_{GS} - V_T - \frac{1}{2} V_{DS}) V_{DS}$$

$$= \frac{10 \ \mu m}{1 \ \mu m} 500 \ cm^2 / V.s \times 2.3 \times 10^{-7} \ F/cm^2 (2.5 - 0.56 - \frac{1}{2} 1 \ V) \times 1 \ V = 1.7 \ mA$$

### 9.4.3 The saturation regime

In the previous section we have developed a simple model for the linear regime of operation of the MOSFET. We found that  $I_D$  depends on  $V_{DS}$  and  $V_{GS}$  and we derived an expression for  $I_D$  that applies up to essentially  $V_{DS} = V_{GS} - V_T$ . What happens if  $V_{DS}$  reaches or exceeds this value? This is the saturation regime.

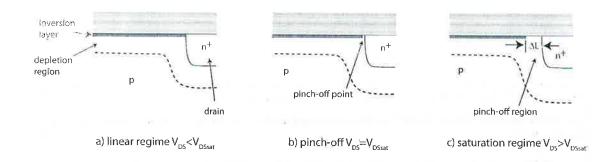

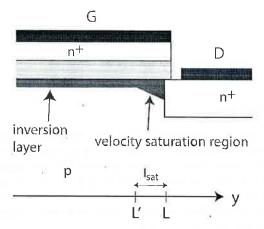

It is clear from our discussion above that around  $V_{DS} = V_{GS} - V_T$ , the electron concentration at the drain-end of the channel drops substantially. In fact, it can become rather small in comparison with the doping level of the body. If this happens, we can think about this as a small depletion region appearing right at the drain end of the channel. This is sketched in Fig. 9.11. This depletion region does not represent in any way a barrier to electron flow. On the contrary, the lateral electric field in this region "pulls" electrons into the drain. <sup>2</sup>

What is significant about the appearance of this depletion region is that if  $V_{DS}$  is increased beyond  $V_{GS} - V_T$ , the extra applied voltage drops entirely in this pinch-off region by widening its lateral extension. This is also sketched in Fig. 9.11. What happens here is entirely analogous to the electrostatics of a reverse biased pn junction that widens as the reverse bias increases. If the pinch-off region widening is small in the scale of the channel length, the electrostatics of the

<sup>&</sup>lt;sup>2</sup>Transport through the pinch-off point in a MOSFET is just like through the base-collector depletion region of a bipolar transistor biased in the forward active regime, as will become clear in Ch. 11.

Figure 9.11: Sketch of electrostatics in MOSFET for different values of  $V_{DS}$ . a) Linear regime:  $V_{DS} < V_{DSsat}$ ; b) pinchoff  $V_{DS} = V_{DSsat}$ ; c) saturation regime  $V_{DS} > V_{DSsat}$ .

channel are not significantly affected by an increase in  $V_{DS}$  past  $V_{GS} - V_T$ . Hence the channel current does not change from the value that it has at  $V_{DS} = V_{GS} - V_T$ . In other words, the drain current has saturated and the MOSFET is said to be in the saturation regime.

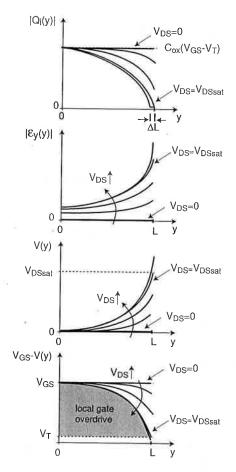

To further clarify the physics of the MOSFET around pinch-off, Fig. 9.12 sketches the inversion layer charge, the lateral electric field, the voltage, and the local gate overdrive along the channel in the linear regime, at pinch-off, and in saturation. The top diagram shows that at pinch-off the inversion charge reaches a minimum at the drain-end of the channel. For higher values of  $V_{DS}$ , the pinch-off point widens and extends slightly into the channel. The third diagram from the top shows that all the extra voltage applied past pinch-off drops in the pinch-off region and that the voltage distribution in the rest of the channel is negligibly affected. This results in a negative gate overdrive in the pinch-off region at the drain end of the channel, as seen in the bottom diagram. The second diagram from the top shows a similar picture for the electric field.

Before we write an expression for the drain current in the saturation regime, we need to discuss several aspects of the pinch-off model that we have just introduced. Current saturation in the pinch-off model has been predicated upon the assumption that a depletion region forms at the drain-end of the channel, that is, that the electron concentration drops below the acceptor concentration in the body. This assumption might be satisfied at low current levels, but it is certain to be violated if the current level is high enough. It turns out that the appearance of a depletion region is not an essential condition for current saturation. Electron velocity saturation at the drain-end of the channel also causes it. Velocity saturation of electrons on the drain side of the channel is likely to occur as the electron concentration drops but current continuity must be maintained. We will understand in the next chapter how velocity saturation causes current saturation.

A second ingredient of current saturation is that the extent of the depletion region (or the velocity saturated region) is small in the scale of the channel length. This of course, depends on the design of the MOSFET. For well designed devices, this is always the case, but proving it requires a detailed model of the two-dimensional electrostatics of the drain-end of the channel.

We can now derive a first-order expression for  $I_{Dsat}$ , the drain current in the saturation

Figure 9.12: Inversion layer charge, lateral electric field, channel voltage and local gate overdrive as a function of location along the channel for a MOSFET for increasing values of  $V_{DS}$ . For  $V_{DS} > V_{DSsat}$ , the electrostatics of the channel are not significantly affected by the increase in  $V_{DS}$  and the channel current is saturated.

regime. Since we argued above that Eq. 9.16 predicts  $I_D$  with good accuracy nearly all the way to  $V_{DS} = V_{GS} - V_T$  and  $I_D$  does not increase beyond this value of  $V_{DS}$ , then  $I_{Dsat}$  can be estimated by substituting  $V_{DS} = V_{GS} - V_T$  in Eq. 9.16 to yield:

$$I_{Dsat} \simeq \frac{W}{2L} \mu_e C_{ox} (V_{GS} - V_T)^2 \tag{9.21}$$

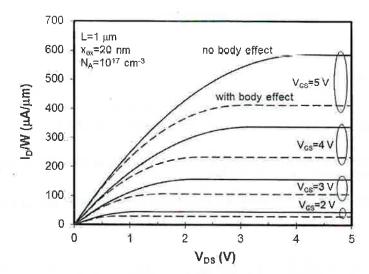

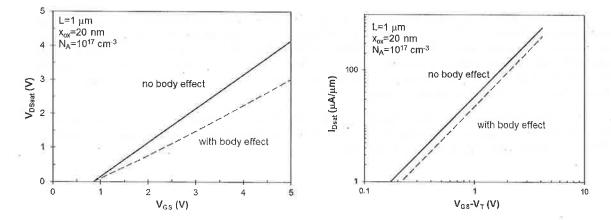

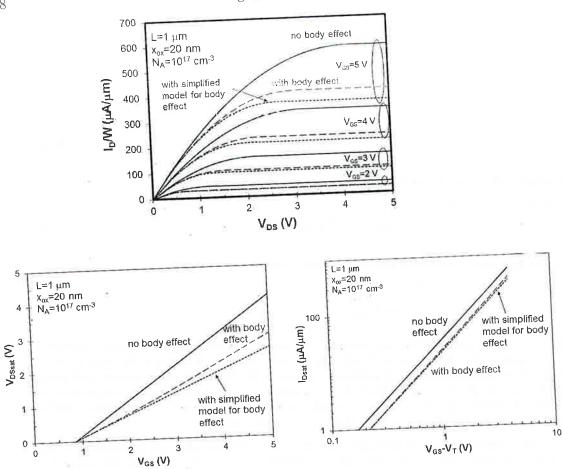

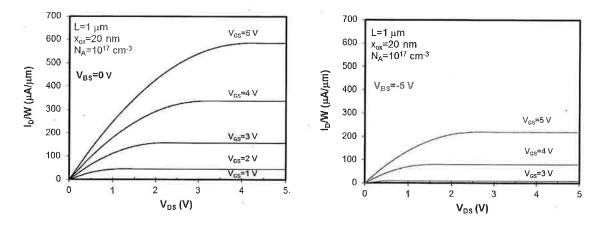

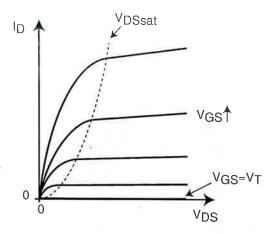

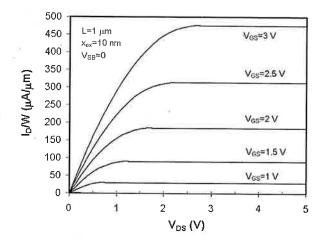

Fig. 9.13 shows the so-called *output characteristics* of the MOSFET. In this graph, the drain current is graphed unchanged with  $V_{DS}$  for  $V_{DS} \ge V_{GS} - V_T$ . This is the manifestation of the saturation regime.

A key result that emerges in Eq. 9.21 is that in the saturation regime, the drain current increases with *the square* of the gate overdrive (the excess gate-to-source voltage above threshold). This is sketched in Fig. 9.14. The reason for the square-law dependence deserves some thought.

Figure 9.13: Sketch of output I-V characteristics of a MOSFET in the linear and saturation regimes.

Figure 9.14: Sketch of transfer characteristics of a MOSFET, that is,  $I_D$  vs.  $V_{GS}$  for different values of  $V_{DS}$ . In the saturation regime,  $I_D$  increases quadratically with gate overdrive. When  $V_{GS}$  exceeds  $V_{DS} + V_T$ , the transistor enters the linear regime and  $I_D$  rises linearly with gate overdrive.

The higher  $V_{GS}$ , the higher the inversion charge in the channel that is available for transport. This is a linear dependence. Additionally, the higher  $V_{GS}$ , the higher the value of  $V_{DS}$  that can be applied before the channel is "pinched-off". As a consequence, when the MOSFET is saturated, the field inside the channel is also higher and the current is also larger. This is also a linear relationship. The combination of both linear dependences results in a square-law dependence for  $I_D$  on  $V_{GS} - V_T$ .

The value of  $V_{DS}$  required to pinch-off the device is commonly referred to as  $V_{DSsat}$ . In the simple formulation derived here,  $V_{DSsat}$  is given by:

$$V_{DSsal} = V_{GS} - V_T (9.22)$$

The locus of  $V_{DSsat}$  in the output characteristics is indicated in Fig. 9.13. As a result of the square-law dependence of  $I_{Dsat}$  on  $V_{GS} - V_T$ , this locus has a parabolic shape.

583

The I-V characteristics of a MOSFET when graphed as in Fig. 9.14 are known as the transfer characteristics. For a given value of  $V_{DS}$ , as  $V_{GS}$  increases above  $V_T$ , the transistor turns on directly into the saturation regime and the current rises quadratically with gate overdrive. As  $V_{GS}$  increases, eventually the transistor is pushed into the linear regime. This happens when  $V_{GSsat} = V_{DS} + V_T$ . Beyond this point,  $I_D$  rises linearly with gate overdrive.

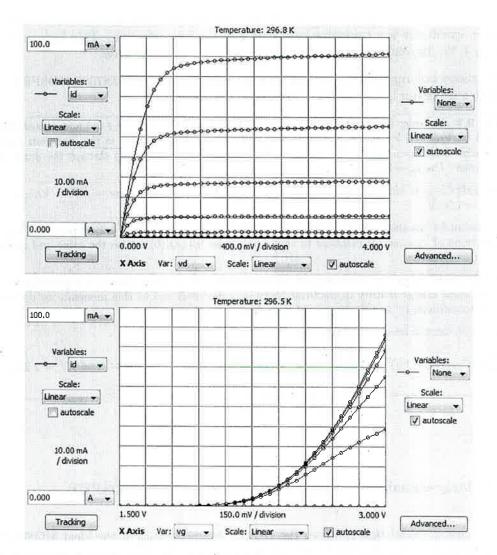

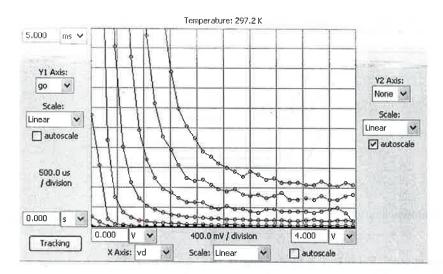

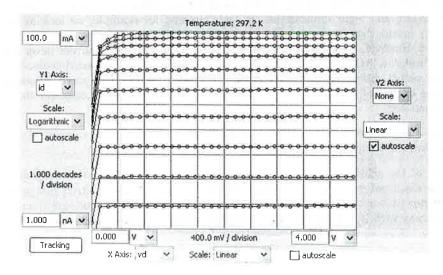

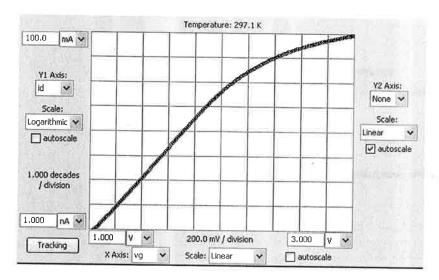

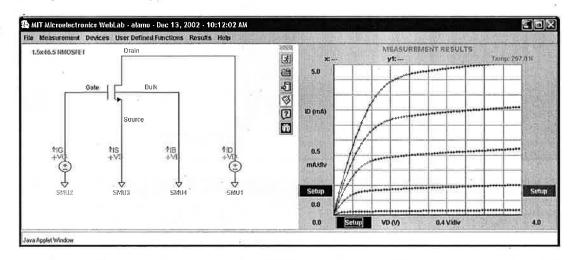

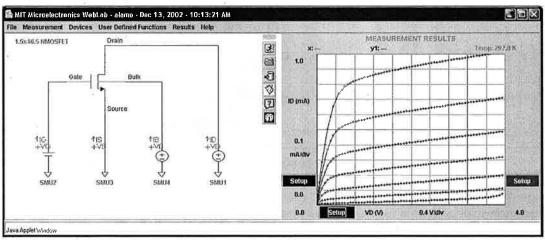

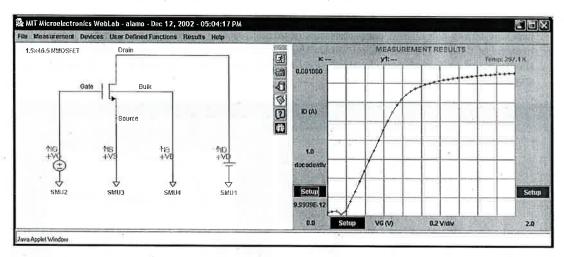

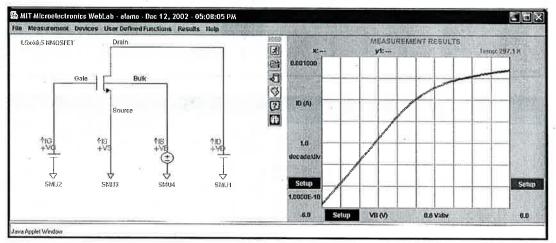

Fig. 9.15 shows experimental output and transfer characteristics of a 2N7000 MOSFET. The behavior of this transistor is very much as discussed in this section.

Exercise 9.2: Consider the same long n-channel MOSFET as in Exercise 9.1 but now biased with  $V_{GS}=2.5~V$ ,  $V_{DS}=4~V$ , and  $V_{BS}=0$ . Estimate the sheet charge density in the inversion layer at the source- and drain-ends of the channel. Estimate the current flowing through the drain of this transistor. Use  $\mu_e=500~cm^2/V.s.$

This transistor is now biased in the saturation regime. This is because  $V_{DS} = 4 \ V > V_{DSsat} = V_{GS} - V_T = 1.94 \ V$ .

The expression for the sheet charge density at the source-end of the channel only depends on  $V_{GS}$ . Since the value of  $V_{GS}$  here is identical to that in Exercise 9.1,  $Q_i(0)$  is also the same and given by  $4.5 \times 10^{-7} \ C/cm^2$ .

With the MOSFET biased in saturation, at the drain-end of the channel there is a pinch-off point. Hence, the sheet charge density of electrons there is quite small and at this moment, we do not know how to estimate it. In Ch. 10 we will learn how to do this.

The drain current can be obtained from Eq. 9.21:

$$I_D = \frac{W}{2L} \mu_e C_{ox} (V_{GS} - V_T)^2 = \frac{10 \ \mu m}{2 \times 1 \ \mu m} 500 \ cm^2 / V.s \times 2.3 \times 10^{-7} \ F/cm^2 (2.5 - 0.56 \ V)^2 = 2.2 \ mA$$

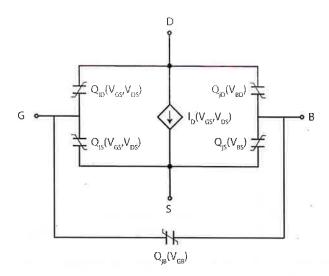

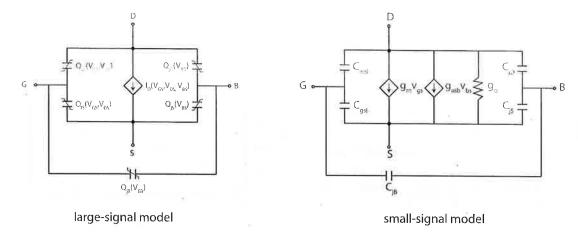

# 9.4.4 DC large-signal equivalent-circuit model of ideal MOSFET

An equivalent circuit model that captures the DC I-V characteristics of the ideal MOSFET is fairly straightforward. In the ideal MOSFET, the drain current also flows through the source and it is controlled by  $V_{DS}$  and  $V_{GS}$ . This behavior can be captured by means of a controlled current source. The dependence of the drain current on  $V_{DS}$  and  $V_{GS}$  is given by Eqs. 9.16 and 9.21 in the linear and saturation regimes, respectively.

In the ideal MOSFET, the gate does not draw any DC current. It is therefore an open circuit. Also, in the ideal MOSFET, we ignore the presence of the source/body and drain/body PN junctions. Hence, the body contact is also an open. The entire DC large-signal equivalent circuit model of the ideal MOSFET is graphed in Fig. 9.16. The diamond shaped current source indicates that this is a dependent source that is controlled by  $V_{GS}$  and  $V_{DS}$ .

Figure 9.15: Measured I-V characteristics of a 2N7000 MOSFET. Top: output characteristics with  $V_{GS}$  stepped from 1 to 3 V in steps of 0.2 V. Bottom: transfer characteristics with  $V_{DS}$  stepped from 0 to 1 V in steps of 0.2 V (screen shots from MIT Microelectronics iLab).

$$G \longrightarrow \bigcup_{D} I_{D}(V_{GS'}V_{DS}) \longrightarrow B$$

Figure 9.16: DC large-signal equivalent circuit model of ideal MOSFET.

### 9.4.5 Energy band diagrams

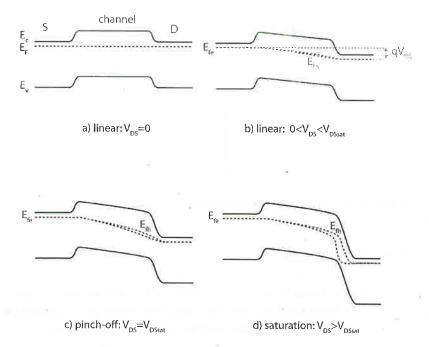

Our understanding of the I-V characteristics of the MOSFET would not be complete without energy band diagrams. Fig. 9.17 sketches energy band diagrams along the semiconductor/insulator interface for a value of  $V_{GS}$  in strong inversion and for several values of  $V_{DS}$ .

In the linear regime with  $V_{DS} = 0$ , the Fermi level is flat along the channel from source to drain. The conduction band is close to the Fermi level in the source and drain but a bit further away in the channel. The bands are flat in the channel.

For a value of  $V_{DS}$  in the linear regime, the electron Fermi level is lowered at the drain with respect to the source by an amount  $qV_{DS}$ . Since the drain is heavily doped, this brings down with it the entire band structure on the drain. A lateral electric field appears in the channel and in consequence, the band structure bends along the channel. Current flows: This also means that the quasi-Fermi level for electrons also tilts along the channel.

At pinch-off, for  $V_{DS} = V_{DSsat}$ , the bending of the bands and the electron quasi-Fermi level along the channel is exacerbated. As one proceeds from source to drain along the channel, the bending increases, although for different reasons.  $E_c$  and  $E_v$  bend because the electric field increases towards the drain end of the channel.  $E_{fe}$  bends because the electron concentration drops towards the drain but the current is constant along the channel. In consequence, the gradient of  $E_{fe}$  must increase as we proceed from source to drain.

In saturation, for  $V_{DS} > V_{DSsat}$ , the band structure and electron quasi-Fermi level along the channel do not change with respect to the situation observed at  $V_{DS} = V_{DSsat}$ . The applied voltage beyond  $V_{DSsat}$ , that is,  $V_{DS} - V_{DSsat}$ , drops entirely at the pinch-off point where the bands and the quasi-Fermi level show a steep dive. It is clear from this diagram that the pinch-off point does not represent at all a bottleneck to the drain current. On the contrary, at the pinch-off point, the electrons are in a "free fall" down the channel to the drain.

In saturation, the bottleneck to the drain current is the energy barrier that electrons at the source have to overcome before they can enter the channel and the electric field at that same point. The energy barrier at the source end of the channel is controlled by  $V_{GS}$ . The higher  $V_{GS}$ , the lower the energy barrier and the higher the concentration of electrons that have enough energy

Figure 9.17: Energy band diagram along semiconductor surface from source to drain for four different values of  $V_{DS}$  (in all cases  $V_{GS} > V_T$ ).

to get injected into the channel. In particular, the height of this energy barrier is independent of what happens down the channel and hence the electron charge at y=0 is independent of  $V_{DS}$ . The tilt of the bands at the source end of the channel determines the electric field there and the velocity at which electrons are extracted from the source. This is set by the potential distribution along the channel. This is unchanged for  $V_{DS} > V_{DSsat}$ , since all the extra voltage applied beyond  $V_{DSsat}$  drops at the pinch-off point.

Fig. 9.17 also shows the quasi-Fermi level for holes along the channel at the different bias conditions. With  $V_{DS}=0$ , both quasi-Fermi levels coincide. As  $V_{DS}$  increases, the quasi-Fermi levels split with  $E_{fh}>E_{fe}$  towards the end of the channel. This is similar to the situation depicted on the right of Fig. 8.29 in which a positive bias is applied between the inversion layer and the body, as will become clear later on in this chapter.

# 9.5 Charge-voltage characteristics of the ideal MOSFET

The I-V characteristics of a MOSFET, as is the case in most semiconductor devices, represent only a partial view of the behavior that is generally relevant in circuit applications. In particular, to capture the dynamics of a MOSFET, we need to complete the picture with the charge-voltage or capacitance-voltage characteristics. These describe the charge that is stored in the device and that must be provided to it or removed from it every time any terminal voltage changes.

In a MOSFET there are two types of stored charge. There is first the depletion charge in

the depletion regions associated with the source-body and drain-body PN junctions as well as the depletion charge in the body of the semiconductor that is associated with the MOS structure itself. In addition to this, there is the electron charge stored in the inversion layer. If  $V_{DS} > 0$ , this charge is in transit from source to drain and results in current. Nevertheless, this is charge that must have been provided once and must be removed if the transistor is to be switched off. We construct first-order models for these two types of stored charge in the next two subsections.

### 9.5.1 Depletion charge

In an ideal MOSFET, as sketched in Fig. 9.3, there are three distinct depletion regions. First, there is the depletion region associated with the source-body PN junction. Second, there is the depletion region associated with the drain-body PN junction. Finally, there is the depletion region associated with the MOS structure itself. The charge-voltage characteristics of these three depletion regions have been studied before in previous chapters.

For the source-body and drain-body junctions, we can recycle results from Sec. 6.4. The charge associated with the source-body depletion region is given by:

$$Q_{jS} = L_S W \sqrt{2q N_A \epsilon_s (\phi_{bij} - V_{BS})} = Q_{jSo} \sqrt{1 - \frac{V_{BS}}{\phi_{bij}}}$$

$$(9.23)$$

where  $L_S$  is the extent of the source in the y dimension,  $\phi_{bij}$  is the built-in potential of the source-body junction.  $Q_{jSo}$  is the depletion charge in thermal equilibrium:

$$Q_{jSo} = L_S W \sqrt{2q N_A \epsilon_s \phi_{bij}} \tag{9.24}$$

In writing Eqs. 9.23 and 9.24, we have assumed that this is an asymmetric junction, that is that the doping level of the source is much higher than that of the body. This is a very good assumption in practice.

Similarly, the depletion charge associated with the drain-body junction is given by:

$$Q_{jD} = L_D W \sqrt{2q N_A \epsilon_s (\phi_{bij} - V_{BD})} = Q_{jDo} \sqrt{1 - \frac{V_{BS} - V_{DS}}{\phi_{bij}}}$$

$$(9.25)$$

with  $Q_{jDo}$  given by:

$$Q_{jDo} = L_D W \sqrt{2q N_A \epsilon_s \phi_{bij}} \tag{9.26}$$

This is equal to  $Q_{jSo}$  if  $L_S = L_D$  as is commonly the case. We have assumed that the doping level on both junctions is the same and that the built-in potential is then identical.

The depletion region charge associated with the MOS structure depends on the regime of operation of the MOSFET. For  $V_{GS} < V_T$ , the MOSFET is in cut-off and there is no inversion

layer anywhere in the channel. In this case, the charge in this depletion region was calculated in Eq. 8.20 and is given by:

$$Q_{jB} = LW \frac{1}{2} \gamma^2 C_{ox} \left[ \sqrt{1 + 4 \frac{V_{GB} - V_{FB}}{\gamma^2}} - 1 \right] - LW \frac{1}{2} \gamma^2 C_{ox} \left[ \sqrt{1 + 4 \frac{V_{GS} - V_{BS} - V_{FB}}{\gamma^2}} - 1 \right]$$

(9.27)

where  $V_{FB}$  is the flatband voltage of the MOS structure. The depletion region charge increases from zero at  $V_{GS} = V_{FB}$  to its maximum value when  $V_{GS} = V_T$ .

For gate voltages in excess of  $V_T$ , an inversion layer is formed under the gate and the depletion region thickness does not increase any more. Hence, for the MOSFET in the linear and saturation regimes, the charge associated with the depletion region in the channel is given by:

$$Q_{jBmax} = LW \frac{1}{2} \gamma^2 C_{ox} \left[ \sqrt{1 + 4 \frac{V_T - V_{BS} - V_{FB}}{\gamma^2}} - 1 \right]$$

(9.28)

When the voltage applied across any of the terminals of a MOSFET changes, the stored depletion charge also changes. This gives rise to capacitive effects. For the source-body and drain-body junctions, the junction capacitances is given, respectively, by:

$$C_{jS} = \frac{C_{jSo}}{\sqrt{1 - \frac{V_{BS}}{\phi_{bij}}}} \tag{9.29}$$

$$C_{jD} = \frac{C_{jDo}}{\sqrt{1 - \frac{V_{BS} - V_{DS}}{\phi_{bij}}}}$$

(9.30)

with

$$C_{jSo} = L_S W \sqrt{\frac{\epsilon_s q N_A}{2\phi_{bij}}} \tag{9.31}$$

$$C_{jDo} = L_D W \sqrt{\frac{\epsilon_s q N_A}{2\phi_{bij}}} \tag{9.32}$$

In the cut-off regime, the depletion region charge underneath the gate is modulated by  $V_{GB}$ . Hence there is also a capacitive effect associated with this. This capacitance is given by:

$$C_{jB} = \frac{LWC_{ox}}{\sqrt{1 + 4\frac{V_{GB} - V_{FB}}{\gamma^2}}}$$

(9.33)

This is a result already obtained in Eq. 8.49. It can also be easily obtained by differentiating Eq. 9.27 with respect to  $V_{GB}$ . This result applies when  $V_{GS} < V_T$ .

When  $V_{GS} > V_T$ , the MOSFET is in the linear or saturation regime and  $Q_{jB}$  becomes independent of  $V_{GB}$ . The associated capacitance is zero.

Exercise 9.3: Consider once again the long n-channel MOSFET of Exercises 9.1 and 9.2. The source and drain regions have a doping level  $N_S = N_D = 10^{19}$  cm<sup>-3</sup> and a length  $L_S = L_D = 5$   $\mu m$ . Estimate the values of  $C_{jS}$ ,  $C_{jD}$  and  $C_{jB}$  at the following two bias points: i)  $V_{GS} = 0$  V,  $V_{DS} = 1$  V, and  $V_{BS} = 0$ , and ii)  $V_{GS} = 2.5$  V,  $V_{DS} = 1$  V, and  $V_{BS} = 0$ .

At the first bias point, the transistor is in cut-off. We start by computing the capacitance per unit area of the source and drain junctions in equilibrium. These are identical and given by Eqs. 9.31 and 9.32. Proceeding as in Ch. 6, we start by calculating the built-in potential of these junctions which we find to be  $\phi_{bij} = 0.94$ . Then:

$$C_{jSo} = C_{jDo} = L_S W \sqrt{\frac{\epsilon_s q N_A}{2\phi_{bij}}} = L_D W \sqrt{\frac{\epsilon_s q N_A}{2\phi_{bij}}}$$

$$= 5 \times 10^{-4} cm \times 10 \times 10^{-4} cm \sqrt{\frac{1.04 \times 10^{-12} F/cm \times 1.6 \times 10^{-19} C \times 10^{17} cm^{-3}}{2 \times 0.94 V}}$$

$$= 4.7 \times 10^{-14} F$$

With  $V_{BS} = 0$ , the capacitance of the source-body junction (Eq. 9.29) is given by the result just obtained:

$$C_{jS} = C_{jSo} = 4.7 \times 10^{-14} F$$

There is a bias applied between the drain and the body.  $C_{jD}$  is then given by (Eq. 9.30):

$$C_{jD} = \frac{C_{jDo}}{\sqrt{1 - \frac{V_{BS} - V_{DS}}{\phi_{bij}}}} = \frac{4.7 \times 10^{-14} F}{\sqrt{1 - \frac{0 - 1 V}{0.94 V}}} = 3.3 \times 10^{-14} F$$

For the first bias point, the capacitance associated with the depletion region of the MOS structure is given by Eq. 9.33:

$$C_{jB} = \frac{LWC_{ox}}{\sqrt{1 + 4\frac{V_{GB} - V_{FB}}{\gamma^2}}} = \frac{1 \times 10^{-4} \ cm \times 10 \times 10^{-4} \ cm \times 2.3 \times 10^{-7} \ F/cm^2}{\sqrt{1 + 4\frac{0 + 1}{0.79^2} \ V}} = 1.8 \times 10^{-14} \ F$$

At the second bias point,  $V_{GS}$  has increased to 2.5 V which is above threshold. Hence, the MOSFET is now in the linear regime and an inversion layer forms. This breaks the electrostatic coupling between the gate and the body and  $C_{jB} = 0$ .

Additionally,  $V_{BS}$  and  $V_{BD}$  are unchanged from the first bias point so  $C_{jS}$  and  $C_{jD}$  have the same values that were obtained at the first bias point.

### 9.5.2 Inversion charge

In addition to the depletion region charge, in a MOSFET in the linear or saturation regimes of operation there is a certain amount of electron charge that is stored in the inversion layer. When

turning on the MOSFET, this charge must be provided, and when turning it off, it has to be removed. The presence of inversion layer charge clearly impacts the dynamics of the MOSFET. In this section, we compute the integrated inversion layer charge for the ideal MOSFET. We also capture its dynamic behavior by means of two intrinsic capacitances.

We seek an expression for the integral of charge in the inversion layer of an ideal MOSFET. This can be expressed mathematically as the integral of  $Q_i$  along the entire channel:

$$Q_I = W \int_0^L Q_i(y) dy \tag{9.34}$$

Since we have derived an expression for  $Q_i$  in terms of V, rather than y, it is best to change variables in this integral and rewrite it as:

$$Q_I = W \int_0^{V_{DS}} Q_i(V) \frac{dy}{dV} dV \tag{9.35}$$

The term in dy/dV can be obtained from Eq. 9.9:

$$\frac{dy}{dV} = -\frac{W\mu_e}{I_D}Q_i(V) \tag{9.36}$$

Combining this with Eq. 9.35, we get:

$$Q_I = -\frac{W^2 \mu_e}{I_D} \int_0^{V_{DS}} Q_i^2(V) dV$$

(9.37)

For the ideal MOSFET,  $Q_i(V)$  was given in Eq. 9.11. Inserting this in Eq. 9.37 yields:

$$Q_{I} = -\frac{W^{2}\mu_{e}C_{ox}^{2}}{I_{D}} \int_{0}^{V_{DS}} (V_{GS} - V - V_{T})^{2} dV = \frac{1}{3}W^{2}\mu_{e}C_{ox}^{2} \frac{(V_{GS} - V_{DS} - V_{T})^{3} - (V_{GS} - V_{T})^{3}}{\frac{W}{L}\mu_{e}C_{ox}(V_{GS} - V_{T} - \frac{1}{2}V_{DS})V_{DS}}$$

(9.38)

After a relatively simple mathematical manipulation  $^{3}$ , we can express  $Q_{I}$  as:

$$Q_I = -\frac{2}{3}WLC_{ox}\frac{(V_{GS} - V_T)^2 + (V_{GS} - V_T)(V_{GD} - V_T) + (V_{GD} - V_T)^2}{(V_{GS} - V_T) + (V_{GD} - V_T)}$$

(9.39)

Note that since we have used Eq. 9.11, this expression is only valid in the linear regime. As was the case of the MOSFET current,  $Q_I$  in the saturation regime can be obtained from this by setting  $V_{DS} = V_{DSsat} = V_{GS} - V_T$ , or  $V_{GD} = V_T$ . This yields:

$$(V_{GS} - V_T - \frac{1}{2}V_{DS})V_{DS} = \frac{1}{2}[(V_{GS} - V_T)^2 - (V_{GD} - V_T)^2]$$

<sup>&</sup>lt;sup>3</sup>Note that:

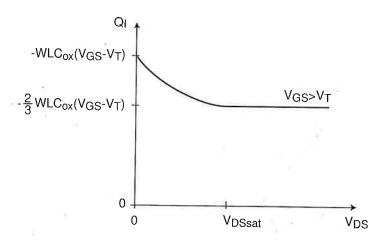

Figure 9.18: Inversion layer charge vs.  $V_{DS}$  for an ideal MOSFET in the linear or saturation regime for a given value of  $V_{GS} > V_T$ .

$$Q_I = -\frac{2}{3}WLC_{ox}(V_{GS} - V_T)$$

(9.40)

This interesting and simple result can be best understood by obtaining also  $Q_I$  in the limit of small  $V_{DS}$ . From Eq. 9.39, we get:

$$Q_I \simeq -WLC_{ox}(V_{GS} - V_T) \tag{9.41}$$

This result makes good sense. In the limit of small  $V_{DS}$ , at any one location in the inversion layer, the charge density is given by  $-C_{ox}(V_{GS}-V_T)$ . Hence, the total charge in the inversion layer can be obtained by multiplying this by the geometrical area of the gate.

The  $\frac{2}{3}$  factor that is present in the expression of the inversion layer charge in the saturation regime in Eq. 9.40 deserves some thinking. If we sketch the inversion charge vs.  $V_{DS}$  for a given value of  $V_{GS} > V_T$ , as in Fig. 9.18, we see that as  $V_{DS}$  increases,  $Q_I$  monotonically decreases from the value given by Eq. 9.41 towards that given by Eq. 9.40. This is the consequence of the channel debiasing that was mentioned earlier. For values of  $V_{GS} > V_T$ , as  $V_{DS}$  increases, the inversion layer charge at any location in the channel, except at the source, gets reduced. This is most prominent towards the end of the channel. This was sketched in the top diagram of Fig. 9.10. Beyond  $V_{DS} = V_{DSsat}$ , the inversion layer charge profile along the channel does not change anymore and  $Q_I$  saturates. This is seen in the top diagram of Fig. 9.12. The factor of  $\frac{2}{3}$  comes from the shape of the evolution of  $Q_i$  with y along the channel.

As we attempt to draw a large-signal equivalent circuit model for the MOSFET that accounts for the charge storage discussed in this section, we encounter an interesting problem. It is clear that the depletion charge storage associated with the source-body junction depletion region,  $Q_{jS}$ , hangs from the source and body terminals. Similarly,  $Q_{jD}$  hangs from the drain and body terminals. Additionally, the depletion charge associated with the MOS depletion region,  $Q_{jB}$ , hangs from the gate and body terminals. The interesting question is what to do about  $Q_{I}$ ?

Figure 9.19: Large-signal equivalent circuit model for ideal MOSFET including depletion charge and inversion charge storage.

One of the terminals of  $Q_I$  is clear, it is the gate. The other terminal is less obvious, since the inversion layer is in contact with both the source and the drain. It then seems that an appropriate way to proceed is to split  $Q_I$  into two components: one that hangs between gate and source, and a second one that hangs between gate and drain. We call these  $Q_{IS}$  and  $Q_{ID}$ , respectively. It is clear that  $Q_I = Q_{IS} + Q_{ID}$ . It is not obvious how to compute  $Q_{IS}$  and  $Q_{ID}$ , individually. In fact, a detailed calculation of  $Q_{IS}$  and  $Q_{ID}$  is a bit involved. Fortunately, as it will become evident below, in many applications we do not need detailed models for  $Q_{IS}$  and  $Q_{ID}$ . It suffices to know the fact that they depend, in general, on both  $V_{GS}$  and  $V_{DS}$ .

The topology of the large-signal equivalent circuit model of the MOSFET incorporating all the storage elements discussed here is shown in Fig. 9.19.

An alternate way to describe the charge-voltage characteristics associated with the inversion layer is through the capacitance. In the case of a microelectronics device with more than two terminals, one has to exercise some caution when defining a capacitance and selecting the terminals across which it is to be placed. The best way to do this is to keep physical insight at all times and to look for the terminals that deliver the charge in both lobes of the charge dipole.

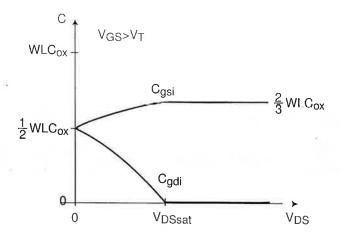

The inversion charge in an ideal MOSFET is supplied by the source and drain. The inversion layer charge is imaged at the gate. The gate charge is delivered by the gate contact. We should therefore expect two capacitors, one placed between the gate and the source and a second one between the gate and the drain. We will refer to these capacitors as  $C_{gsi}$  and  $C_{gdi}$  where the i refers to the intrinsic device.  $C_{gsi}$  and  $C_{gdi}$  can be easily obtained by computing suitable derivatives of  $Q_I$  in Eq. 9.39 with respect to the appropriate terminal voltages, holding all other voltages constant:

$$C_{gsi} = -\frac{\partial Q_I}{\partial V_{GS}}|_{V_{GD}} = \frac{1}{2}WLC_{ox}(V_{GS} - V_T)\frac{V_{GS} - V_T - \frac{2}{3}V_{DS}}{(V_{GS} - V_T - \frac{1}{2}V_{DS})^2}$$

(9.42)

$$C_{gdi} = -\frac{\partial Q_I}{\partial V_{GD}}|_{V_{GS}} = \frac{1}{2}WLC_{ox}(V_{GS} - V_{DS} - V_T) \frac{V_{GS} - V_T - \frac{1}{3}V_{DS}}{(V_{GS} - V_T - \frac{1}{2}V_{DS})^2}$$

(9.43)

As was the case of Eq. 9.39, these expressions only hold for the linear regime. For  $V_{DS} = V_{DSsat}$ , they become:

$$C_{gsi} = \frac{2}{3}WLC_{ox} (9.44)$$

$$C_{gdi} = 0 (9.45)$$

which are the appropriate values for the saturation regime  $(V_{DS} > V_{DSsat})$ . For very small  $V_{DS}$ , it is interesting to see that:

$$C_{gsi} \simeq C_{gdi} \simeq \frac{1}{2} W L C_{ox} \tag{9.46}$$

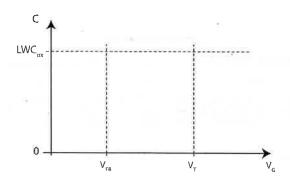

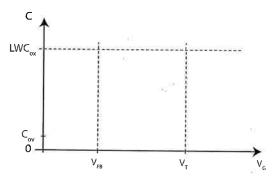

The evolution of  $C_{gsi}$  and  $C_{gdi}$  with  $V_{DS}$  is shown in Fig. 9.20. This behavior makes good physical sense. For small  $V_{DS}$ , we have a very symmetric situation where the charge in the inversion layer splits even between the source and the drain. As  $V_{DS}$  increases, the electrostatic influence of  $V_{GD}$  wanes, while that of  $V_{GS}$  strengthens. At  $V_{DS} = V_{DSsat}$ , the drain loses control of the inversion layer charge and  $C_{gdi} = 0$ . The channel has been pinched off. For higher values of  $V_{DS}$ , the picture does not change.

Figure 9.20:  $C_{gsi}$  and  $C_{gdi}$  vs.  $V_{DS}$  for an ideal MOSFET in the linear and saturation regimes for a given value of  $V_{GS} > V_T$ .

Exercise 9.4: Consider once again the long n-channel MOSFET of Exercises 9.1-9.3. Estimate the values of  $C_{gsi}$  and  $C_{gdi}$  at the following three bias points: i)  $V_{GS}=2.5~V,~V_{DS}=0~V$ , and  $V_{BS}=0$ ; ii)  $V_{GS}=2.5~V,~V_{DS}=4~V$ , and  $V_{BS}=0$ .

We start by computing the geometrical capacitance of the gate. This is given by:

$$C_g = LWC_{ox} = 1 \times 10^{-4} \text{ cm} \times 10 \times 10^{-4} \text{ cm} \times 2.3 \times 10^{-7} \text{ F/cm}^2 = 2.3 \times 10^{-14} \text{ F}$$

At the first bias point, the transistor is in the linear regime with  $V_{DS} = 0$ . Hence, the geometrical capacitance of the gate is split equally between the source and drain. Then:

$$C_{gsi} = C_{gdi} = \frac{1}{2}LWC_{ox} = 1.2 \times 10^{-14} F$$

At the second bias point, the MOSFET is in the linear regime. Hence we have to use expressions 9.42 and 9.43. For  $C_{gsi}$ , we have:

$$C_{gsi} = \frac{1}{2}WLC_{ox}(V_{GS} - V_T) \frac{V_{GS} - V_T - \frac{2}{3}V_{DS}}{(V_{GS} - V_T - \frac{1}{2}V_{DS})^2}$$

$$= 1.2 \times 10^{-14} F(2.5 - 0.56 V) \frac{2.5 - 0.56 - \frac{2}{3} \times 1 V}{(2.5 - 0.56 - \frac{1}{2} \times 1 V)^2} = 1.4 \times 10^{-14} F$$

Proceeding in a similar way with Eq. 9.43, we obtain  $C_{gdi} = 8.8 \times 10^{-15} F$ .

At the third bias point, the MOSFET is in saturation. Hence, according to Eq. 9.44,  $C_{gsi}$  is given by:

$$C_{gsi} = \frac{2}{3}WLC_{ox} = \frac{2}{3}2.3 \times 10^{-14} \ F = 1.5 \times 10^{-14} \ F$$

And  $C_{gdi} = 0 \text{ (Eq. 9.45)}_{*}$

Figure 9.21: Illustration showing how a mixed-signal situation can be studied using the large-signal equivalent circuit model developed in the previous section.

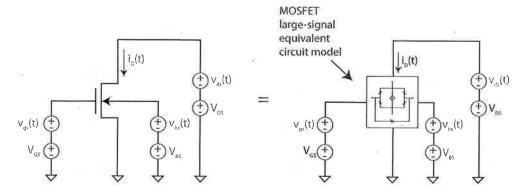

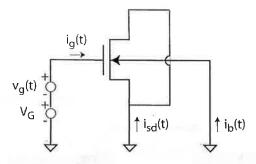

## 9.6 Small-signal behavior of ideal MOSFET

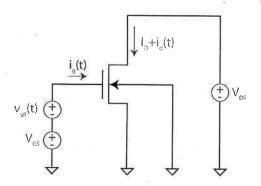

In analog and mixed-signal applications, MOSFETs are often used in the small-signal mode. In these situations, the device is biased by means of DC sources in some regime, typically saturation, and then a small signal is applied to one or more terminals. There is interest in evaluating the response of the device to the small-signals alone. In a general way, we can consider these kinds of situations as on the left of Fig. 9.21. This figure shows a MOSFET biased through three DC voltage sources,  $V_{GS}$ ,  $V_{DS}$ , and  $V_{BS}$ , referred to the source. In addition, three small-signal sources:  $v_{gs}(t)$ ,  $v_{ds}(t)$ , and  $v_{bs}(t)$ , are also applied as shown. In general, we are interested in the time dependent drain current,  $i_D(t)$ , that results.

The equivalent circuit model that we developed in the previous section can certainly be used to solve this problem. This is illustrated in Fig. 9.21. In this approach, the transistor is substituted by its equivalent circuit model and standard circuit solving techniques are used to determine  $i_D(t)$ . However, since the model elements are non-linear, this approach can become quite tedious. Fortunately, many circuit simulation tools, such as SPICE, are available to solve the problem this way. In this approach, actual waveforms are introduced to a device model and the output waveforms are computed. A problem with this approach is that it is hard to develop an intuitive understanding for the connection among the figures of merit of interest, such as amplitude and phase of the drain current waveform, and the bias point or the device parameters. Fortunately, for a class of problems referred to as "small-signal problems," there is a more expeditious and intuitive approach.

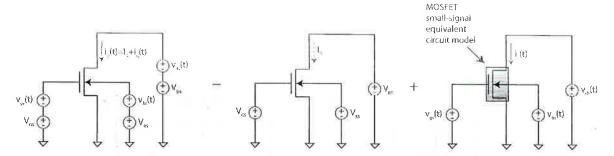

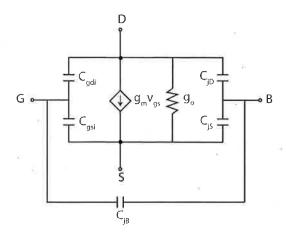

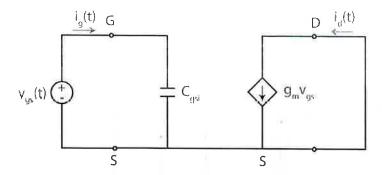

### 9.6.1 Small-signal equivalent circuit model of ideal MOSFET

If the amplitude of the small signals is small enough, superposition suggests that the time-dependent response of the device,  $i_D(t)$ , should be the sum of the DC bias current  $I_D$  that is imposed by the DC voltage sources plus a small time dependent component  $i_d(t)$ . This is sketched in Fig. 9.22. Mathematically, this can be expressed as:

$$i_D(V_{GS}, V_{DS}, V_{BS}; v_{gs}, v_{ds}, v_{bs}) \simeq I_D(V_{GS}, V_{DS}, V_{BS}) + i_d(V_{GS}, V_{DS}, V_{BS}; v_{gs}, v_{ds}, v_{bs})$$

(9.47)

Note how the small-signal response in general depends on the bias point that is selected.

Figure 9.22: Illustration of superposition as a way to break a mixed-signal situation (left) into a DC bias situation (center) plus a small-signal situation (right).

The small-signal equivalent circuit model of the MOSFET is a circuit representation of the set of dependencies of the small-signal current  $i_d(t)$  on the small-signal voltages  $v_{gs}$ ,  $v_{ds}$ , and  $v_{bs}$ . This is the gray box on the figure on the right of Fig. 9.22. Since the small-signal sources are of small magnitude, the non-linear behavior of the MOSFET gets linearized. Linearity then allows us to express  $i_d(t)$  as the sum of three independent terms in each of the small-signal voltage sources:

$$i_d(V_{GS}, V_{DS}, V_{BS}; v_{gs}, v_{ds}, v_{bs})$$

$$= i_d(V_{GS}, V_{DS}, V_{BS}; v_{gs}) + i_d(V_{GS}, V_{DS}, V_{BS}; v_{ds}) + i_d(V_{GS}, V_{DS}, V_{BS}; v_{bs})$$

(9.48)

Depending on the complexity of the small-signal equivalent circuit model, this approach to solving the problem can be fairly fast and yield very meaningful analytical results. So the key question is: what is a suitable small-signal equivalent circuit model for the MOSFET? Since we already have a large-signal equivalent circuit model (Fig. 9.19), this requires only that we linearize it. This is fairly straightforward. In the first step, the charge storage elements become simple capacitors. Their expressions were already derived in the previous section. We are then left to deal with the non-linear voltage-controlled current source.

In a most general way, linearizing  $I_D$  demands that we take the linear terms of its Taylor series expansion:

$$i_{D}(V_{GS}, V_{DS}, V_{BS}; v_{gs}, v_{ds}, v_{bs})$$

$$\simeq I_{D}(V_{GS}, V_{DS}, V_{DS}, V_{BS}) + \left(\frac{\partial I_{D}}{\partial V_{GS}}|_{V_{DS}, V_{BS}}\right) v_{gs} + \left(\frac{\partial I_{D}}{\partial V_{DS}}|_{V_{GS}, V_{BS}}\right) v_{ds} + \left(\frac{\partial I_{D}}{\partial V_{BS}}|_{V_{GS}, V_{DS}}\right) v_{bs}$$

$$= I_{D} + g_{m} v_{gs} + g_{o} v_{ds} + g_{mb} v_{bs}$$

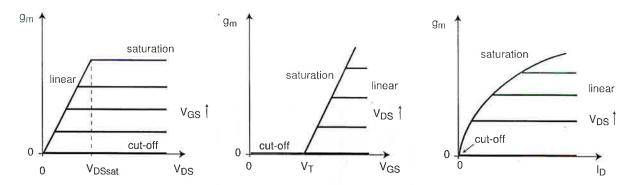

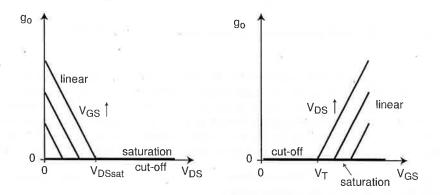

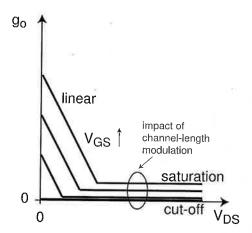

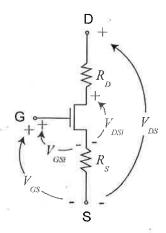

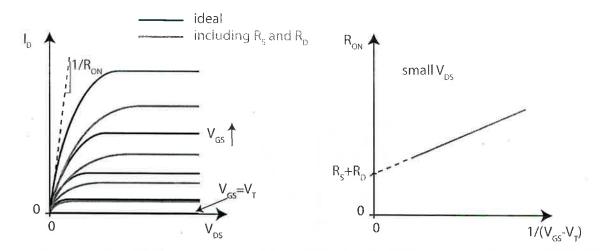

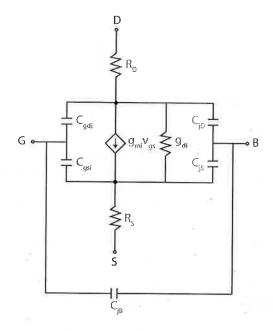

(9.49)